Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

# **COURSE FILE**

ON

## **ELECTRONIC DEVICES AND CIRCUITS**

Course Code - EC301PC

II B.Tech I-SEMESTER A.Y.: 2022-2023

**Prepared by**

Mr. K. RAJENDER Assistant Professor

Head of the Department Electronics and Communication Engg. Dept SRI INDU INSTITUTE OF ENGG & TECH Sheriguda(V), Ibrahimpatham(M), R.R.Dist-501 510

PRINCIPAL Sri Indu Institute of Engineering & Tect. Sheriguda(Vill), Ibrahimpatnam

R.R. Dist. Telangana-501 510.

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

| Academic Year    | 2022-2023                            |

|------------------|--------------------------------------|

| Course Title     | ELECTRONIC DEVICES AND CIRCUITS      |

| Course Code      | EC301PC                              |

| Programme        | B.Tech                               |

| Year & Semester  | II year I-semester                   |

| Branch & Section | ECE-A                                |

| Regulation       | R18                                  |

| Course Faculty   | Mr. K. RAJENDER, Assistant Professor |

### **Index of Course File**

| S. No. | Name of the content                                                            |

|--------|--------------------------------------------------------------------------------|

| 1      | Institute vision and mission                                                   |

| 2      | Department vision and mission                                                  |

| 3      | Program Educational Objectives/ Program Specific Outcomes                      |

| 4      | Program Outcomes                                                               |

| 5      | Course Syllabus with Structure                                                 |

| 6      | Course Outcomes (CO)                                                           |

| 7      | Mapping CO with PO/PSO and Justification                                       |

| 8      | Academic Calendar                                                              |

| 9      | Time table - highlighting your course periods including tutorial               |

| 10     | Lesson plan with number of hours/periods, TA/TM, Text/Reference book           |

| 11     | Web references                                                                 |

| 12     | Lecture notes                                                                  |

| 13     | List of Power point presentations                                              |

| 14     | University Question papers                                                     |

| 15     | Internal Question papers, Key with CO and BT                                   |

| 16     | Assignment Question papers mapped with CO and BT                               |

| 17     | Tutorial topics                                                                |

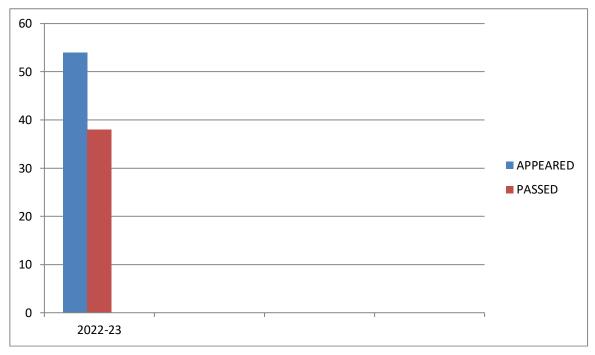

| 18     | Result Analysis to identify weak and advanced learners - 3 times in a semester |

| 19     | Result Analysis at the end of the course                                       |

| 20     | Remedial class for weak students - schedule and evidences                      |

| 21     | CO, PO/PSO attainment sheets                                                   |

| 22     | Attendance register                                                            |

| 23     | Course file (Digital form)                                                     |

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

### INSTITUTE VISION AND MISSION

### Vision:

To become a premier institute of academic excellence by providing the world class education that transforms individuals into high intellectuals, by evolving them as empathetic and responsible citizens through continuous improvement.

### Mission:

- IM1: To offer outcome-based education and enhancement of technical and practical skills.

- **IM2:** To Continuous assess of teaching-learning process through institute-industry collaboration.

- **IM3:** To be a centre of excellence for innovative and emerging fields in technology development with state-of-art facilities to faculty and students' fraternity.

- **IM4:** To Create an enterprising environment to ensure culture, ethics and social responsibility among the stakeholders.

Head of the Department Electronics and Communication Engg. Dept SRI INDU INSTITUTE OF ENGG & TECH Sheriguda(V), Ibrahimpatnam(M), R.R.Dist-501 510

PRINCIPAL

Sri Indu Institute of Engineering & Tech Sheriguda(Vill), Ibrahimpatnam R.R. Dist. Telangana-501 510.

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### DEPARTMENT VISION AND MISSION

### Vision:

To become a recognized center in the field of Electronics and Communication Engineering by producing creative engineers with social responsibility and address ever-changing global challenges.

### Mission:

- **DM1:** To facilitate an academic environment that enables student's centric learning.

- **DM2:** To provide state-of-the-art hardware and software technologies to meet industry requirements.

- DM3: To continuously update the Academic and Research infrastructure.

- **DM4:** To Conduct Technical Development Programs for overall professional caliber of Stake Holders.

Head of the Department Electronics and Communication Engg. Dept SRI INDU INSTITUTE OF ENGG & TECH Sheriguda(V), Ibrahimpatham(M), R.R.Dist-501 510

Sri Indu Institute of Engineering & Tech Sheriguda(Vill), Ibrahimpatnam R.R. Dist. Telangana-501 510.

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

### **PROGRAM EDUCATIONAL OBJECTIVES**

Program Educational objectives are to Promote:

- **PEO1:** Graduates with a strong foundation in Electronics and Communication Engineering, Science and Technology to become successful in the chosen professional career.

- **PEO2:** Graduates with ability to execute innovative ideas for Research and Development with continuous learning.

- PEO3: Graduates inculcated with industry based soft-skills to enable employability.

- **PEO4:** Graduates demonstrate with ability to work in interdisciplinary teams and ethical professional behavior.

### **PROGRAM SPECIFIC OUTCOMES**

**PSO 1: Design Skills:** Design, analysis and development a economical system in the area of Embedded system & VLSI design.

**PSO 2: Software Usage:** Ability to investigate and solve the engineering problems using MATLAB, Keil and Xilinx.

Head of the Department Electronics and Communication Engg. Dept SRI INDU INSTITUTE OF ENGG & TECH Shenguda(V), Ibrahimpatham(M), R.R.Dist-501 510

RINCIPAL Sri Indu Institute of Engineering & Tech Sheriguda(Vill), Ibrahimpatnam

R.R. Dist. Telangana-501 510.

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

Recognized Under 2(f) of UGC Act 1956 Approved by AICTE, New Delhi Affiliated to JNTUH, Hyderabad.

### **PROGRAM OUTCOMES**

1. **ENGINEERING KNOWLEDGE**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

2. **PROBLEM ANALYSIS**: Identify, formulate, research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

3. **DESIGN/DEVELOPMENT OF SOLUTIONS**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

4. **CONDUCT INVESTIGATIONS OF COMPLEX PROBLEMS**: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

5. **MODERN TOOL USAGE**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modelling to complex engineering activities with an understanding of the limitations.

6. **THE ENGINEER AND SOCIETY**: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

7. **ENVIRONMENT AND SUSTAINABILITY**: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

8. **ETHICS**: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

9. **INDIVIDUAL AND TEAM WORK**: Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

10. **COMMUNICATION**: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, give and receive clear instructions.

11. **PROJECT MANAGEMENT AND FINANCE**: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

12. **LIFE-LONG LEARNING**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

Main Road, Sheriguda, Ibrahimpatnam, R.R. Dist. 501 510. Campus Ph:9640590999, 9347187999, 8096951507.

### JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABADB.Tech. in ELECTRONICS AND COMMUNICATION ENGINEERING COURSE STRUCTURE & SYLLABUS (R18) Applicable From 2018-19 Admitted Batch

### II YEAR I SEMESTER

| S. No. | Course<br>Code | Course Title                        | L  | T | P | Credits |

|--------|----------------|-------------------------------------|----|---|---|---------|

| 1      | EC301PC        | Electronic Devices and Circuits     | 3  | 1 | 0 | 4       |

| 2      | EC302PC        | Network Analysis and Transmission   | 3  | 0 | 0 | 3       |

|        |                | Lines                               |    |   |   |         |

| 3      | EC303PC        | Digital System Design               | 3  | 1 | 0 | 4       |

| 4      | EC304PC        | Signals and Systems                 | 3  | 1 | 0 | 4       |

| 5      | EC305ES        | Probability Theory and Stochastic   | 3  | 0 | 0 | 3       |

|        |                | Processes                           |    |   |   |         |

| 6      | EC306PC        | Electronic Devices and Circuits Lab | 0  | 0 | 2 | 1       |

| 7      | EC307PC        | Digital System Design Lab           | 0  | 0 | 2 | 1       |

| 8      | EC308ES        | Basic Simulation Lab                | 0  | 0 | 2 | 1       |

| 9      | *MC309         | Constitution of India 3 0           |    |   |   | 0       |

|        |                | Total Credits                       | 18 | 3 | 6 | 21      |

### II YEAR II SEMESTER

| S. No. | Course<br>Code | Course Title                            | L  | Т | Р  | Credits |

|--------|----------------|-----------------------------------------|----|---|----|---------|

| 1      | MA401BS        | Laplace Transforms, Numerical Methods & | 3  | 1 | 0  | 4       |

|        |                | Complex Variables                       |    |   |    |         |

| 2      | EC402PC        | Electromagnetic Fields and Waves        | 3  | 0 | 0  | 3       |

| 3      | EC403PC        | Analog and Digital Communications       | 3  | 1 | 0  | 4       |

| 4      | EC404PC        | Linear IC Applications                  | 3  | 0 | 0  | 3       |

| 5      | EC405PC        | Electronic Circuit Analysis             | 3  | 0 | 0  | 3       |

| 6      | EC406PC        | Analog and Digital Communications Lab   | 0  | 0 | 3  | 1.5     |

| 7      | EC407PC        | IC Applications Lab                     | 0  | 0 | 3  | 1.5     |

| 8      | EC408PC        | Electronic Circuit Analysis Lab         | 0  | 0 | 2  | 1       |

| 9      | *MC409         | Gender Sensitization Lab0020            |    |   |    | 0       |

|        |                | Total Credits                           | 15 | 2 | 10 | 21      |

\*MC – Satisfactory/Unsatisfactory

### EC301PC: ELECTRONIC DEVICES AND CIRCUITS

#### B.Tech. II Year I Sem.

#### **Course Objectives:**

- To introduce components such as diodes, BJTs and FETs.

- To know the applications of components.

- To know the switching characteristics of components

- To give understanding of various types of amplifier circuits

Course Outcomes: Upon completion of the Course, the students will be able to:

- Know the characteristics of various components.

- Understand the utilization of components.

- Understand the biasing techniques

- Design and analyze small signal amplifier circuits.

#### UNIT - I

**Diode and Applications:** Diode - Static and Dynamic resistances, Equivalent circuit, Load line analysis, Diffusion and Transition Capacitances, Diode Applications: Switch-Switching times.

Rectifier - Half Wave Rectifier, Full Wave Rectifier, Bridge Rectifier, Rectifiers with Capacitive and Inductive Filters, Clippers-Clipping at two independent levels, Clamper-Clamping Circuit Theorem, Clamping Operation, Types of Clampers.

#### UNIT - II

**Bipolar Junction Transistor (BJT):** Principle of Operation, Common Emitter, Common Base and Common Collector Configurations, Transistor as a switch, switching times, Transistor Biasing and Stabilization - Operating point, DC & AC load lines, Biasing - Fixed Bias, Self Bias, Bias Stability, Bias Compensation using Diodes.

#### UNIT - III

**Junction Field Effect Transistor (FET):** Construction, Principle of Operation, Pinch-Off Voltage, Volt-Ampere Characteristic, Comparison of BJT and FET, Biasing of FET, FET as Voltage Variable Resistor. **Special Purpose Devices:** Zener Diode - Characteristics, Voltage Regulator. Principle of Operation -SCR, Tunnel diode, UJT, Varactor Diode.

#### $\mathbf{UNIT}-\mathbf{IV}$

Analysis and Design of Small Signal Low Frequency BJT Amplifiers: Transistor Hybrid model, Determination of h-parameters from transistor characteristics, Typical values of h- parameters in CE, CB and CC configurations, Transistor amplifying action, Analysis of CE, CC, CB Amplifiers and CE Amplifier with emitter resistance, low frequency response of BJT Amplifiers, effect of coupling and bypass capacitors on CE Amplifier.

#### $\mathbf{UNIT}-\mathbf{V}$

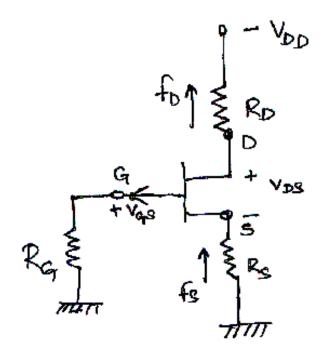

**FET Amplifiers:** Small Signal Model, Analysis of JFET Amplifiers, Analysis of CS, CD, CG JFET Amplifiers. MOSFET Characteristics in Enhancement and Depletion mode, Basic Concepts of MOS Amplifiers.

#### **TEXT BOOKS:**

- 1. Electronic Devices and Circuits- Jacob Millman, McGraw Hill Education

- 2. Electronic Devices and Circuits theory– Robert L. Boylestead, Louis Nashelsky, 11th Edition,2009, Pearson.

#### **REFERENCE BOOKS:**

- 1. The Art of Electronics, Horowitz, 3<sup>rd</sup> Edition Cambridge University Press

- 2. Electronic Devices and Circuits, David A. Bell 5<sup>th</sup> Edition, Oxford.

- 3. Pulse, Digital and Switching Waveforms –J. Millman, H. Taub and Mothiki S. Prakash Rao, 2Ed.,2008, Mc Graw Hill.

L T P C 3 1 0 4

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

### **Course: Electronic Devices and Circuits (C211) Course Outcomes**

**Class: II ECE-A**

After completing this course the student will be able to:

| C211.1 | Ability to analyze the diode under various applications such | Creating, Applying,      |

|--------|--------------------------------------------------------------|--------------------------|

|        | as rectifier, clippers, clamper Circuits.                    | Analyzing                |

| C211.2 | Ability to Classify various configurations and analyze the   | Understanding Analyzing, |

|        | need for stabilization and biasing techniques of BJT.        | Applying                 |

| C211.3 | Ability to Discuss operation, biasing and applications of    | Understanding, Applying, |

|        | JFET.                                                        | Evaluating               |

| C211.4 | Ability to Demonstrate special purpose devices like Zener,   | Understanding, Applying  |

|        | Tunnel, varactor diode, UJT,SCR.                             |                          |

| C211.5 | Ability to design and analyze the Small signal low           | Understanding, Creating, |

|        | frequency of BJT amplifiers                                  | Applying                 |

| C211.6 | Ability to Design and analyze FET amplifiers                 | Understanding, Creating, |

|        |                                                              | Applying                 |

### Mapping of course outcomes with program outcomes:

High -3 Medium -2 Low-1

| PO / CO | PO   | PSO  | PSO  |

|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

|         | 1    | 2    | 3    | 4    | 5    | 6    | 7    | 8    | 9    | 10   | 11   | 12   | 1    | 2    |

| C211.1  | 3    | 2    | -    | -    | 3    | 1    | 1    | 1    | -    | 2    | 2    | 3    | 3    | 3    |

| C211.2  | -    | 1    | 3    | -    | -    | 1    | 1    | 1    | -    | 2    | 2    | 2    | 3    | 3    |

| C211.3  | 1    | 3    | -    | -    | 2    | 1    | 1    | 1    | -    | 2    | 2    | -    | 3    | 3    |

| C211.4  | 2    | -    | 2    | 2    | -    | 1    | 1    | 1    | -    | 2    | 2    | 3    | 3    | 3    |

| C211.5  | 2    | 3    | 3    | -    | 3    | 1    | 1    | 1    | 2    | 2    | 2    | 2    | 3    | 3    |

| C211.6  | 3    | 3    | -    | -    | 3    | 1    | 1    | 1    | 2    | 2    | 2    | 3    | 3    | 3    |

| C211    | 2.20 | 2.40 | 2.67 | 2.00 | 2.75 | 1.00 | 1.00 | 1.00 | 2.00 | 2.00 | 2.00 | 2.60 | 3.00 | 3.00 |

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

### **Course: Electronic Devices and Circuits (C211)**

**Class: II ECE-A**

**P01.ENGINEERING KNOWLEDGE**: Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

**P02.PROBLEM ANALYSIS**: Identify, formulate, research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**P03.DESIGN/DEVELOPMENT OF SOLUTIONS**: Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations

### PO 4.CONDUCT INVESTIGATIONS OF COMPLEX PROBLEMS: Use research-based

Knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

**P05.MODERN TOOL USAGE**: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

**PO6:THE ENGINEER AND SOCIETY:** Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

**PO7:ENVIRONMENT AND SUSTAINABILITY:** Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

**PO8: ETHICS:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

**PO9:INDIVIDUAL AND TEAM WORK:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

**PO10: COMMUNICATION:** Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

**PO11:PROJECT MANAGEMENT AND FINANCE:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

**PO12.LIFE-LONG LEARNING**: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

**PSO1: DESIGN SKILLS:** Design, analysis and development a economical system in the area of Embedded system & VLSI design

**PSO2: SOFTWARE USAGE:** Ability to investigate and solve the engineering problems using MATLAB, Keil and Xilinx.

### **<u>CO-PO mapping Justification</u>**

C211.1 Ability to analyze the diode under various applications such as rectifier, clippers, clamper Circuits. (Creating, Applying, Analyzing)

|      | Justification                                                                                                                                                                                                                                                                                                          |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO1  | The ability to analyze diodes in various applications involves applying a solid foundation in mathematics, science, and engineering fundamentals. Engineers use this knowledge to design and troubleshoot circuits, ensuring that diodes function effectively in rectifiers, clippers, and clamper circuits. (level 3) |

| PO2  | Students can analyze the rectifier, clippers, clamper Circuits using loop equations. (level 2)                                                                                                                                                                                                                         |

| PO5  | Students can design different basic electronic circuits with the knowledge of clippers, clampers, rectifiers. (level 1)                                                                                                                                                                                                |

| PO6  | Engineers must be aware of the broader impact of their work and strive to balance technical excellence with social responsibility. (level 1)                                                                                                                                                                           |

| PO7  | Students must know that engineers need to consider the efficiency, reliability, and environmental impact of these circuits during the design and analysis phase. (level 1)                                                                                                                                             |

| PO8  | Students can gain knowledge that engineers must prioritize integrity, safety, environmental responsibility, social impact, and transparency in their designs and analyses, ensuring that their work aligns with the highest standards of professional ethics in the field of engineering. (level 1)                    |

| PO10 | Engineers should engage in discussions, share insights, and contribute to the collective knowledge base, fostering an environment of collaboration and innovation in diode analysis and related fields. (level 2)                                                                                                      |

| PO11 | Students can get demonstrate knowledge and understanding of the electronic devices and circuits and apply these to one's own project, as a member and leader in a team, to manage projects and in multidisciplinary environments.(level 2)                                                                             |

| PO12 | Students can continuously learning to explore more knowledge in semiconductor devices. (level 2)                                                                                                                                                                                                                       |

| PSO1 | Students are able to explore the design of electronic devices in the areas of VLSI design and embedded systems. (level 3)                                                                                                                                                                                              |

| PSO2 | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)                                                                                                                                                                                                                           |

C211.2 Ability to classify various configurations and analyze the need for stabilization and biasing techniques of BJT. (Understanding Analyzing, Applying)

|      | Justification                                                                                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO2  | Students can learn the operation of transistor in different biasing configurations. (level 1)                                                                                                                                                                                                       |

| PO3  | Students can design the different transistor configuration circuits.(level 3)                                                                                                                                                                                                                       |

| PO6  | Engineers must be aware of the broader impact of their work and strive to balance technical excellence with social responsibility. (level 1)                                                                                                                                                        |

| PO7  | Students must know that engineers need to consider the efficiency, reliability, and environmental impact of these circuits during the design and analysis phase. (level 1)                                                                                                                          |

| PO8  | Students can gain knowledge that engineers must prioritize integrity, safety, environmental responsibility, social impact, and transparency in their designs and analyses, ensuring that their work aligns with the highest standards of professional ethics in the field of engineering. (level 1) |

| PO10 | Effective communication through written materials ensures that the rationale,<br>methodologies, and outcomes of BJT analysis are understood by diverse audiences within<br>the engineering community and beyond. (level 2)                                                                          |

| PO11 | Students can get demonstrate knowledge and understanding of the electronic devices<br>and circuits and apply these to one's own project, as a member and leader in a team, to<br>manage projects and in multidisciplinary environments.(level 2)                                                    |

| PO12 | Students can continuously learning to explore more knowledge in semiconductor devices. (level 3)                                                                                                                                                                                                    |

| PSO1 | Students are able to explore the design of electronic devices in the areas of VLSI design and embedded systems. (level 3)                                                                                                                                                                           |

| PSO2 | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)                                                                                                                                                                                                        |

# C211.3 Ability to Discuss operation, biasing and applications of JFET. (Understanding, Analyzing, Evaluating)

|      | Justification                                                                                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO1  | Students are able to understand the basic knowledge of FET. (level 1).                                                                                                                                                                                                                              |

| PO2  | Students can analyze the operation of different electronic devices. (level 3)                                                                                                                                                                                                                       |

| PO5  | Students can apply different biasing techniques in the design of FETs (Field-Effect Transistors) (level 2).                                                                                                                                                                                         |

| PO6  | Student must know an engineer's must be aware of the broader impact of their work and strive to balance technical excellence with social responsibility. (level 1)                                                                                                                                  |

| PO7  | Students must know that engineers need to consider the efficiency, reliability, and environmental impact of these circuits during the design and analysis phase. (level 1)                                                                                                                          |

| PO8  | Students can gain knowledge that engineers must prioritize integrity, safety, environmental responsibility, social impact, and transparency in their designs and analyses, ensuring that their work aligns with the highest standards of professional ethics in the field of engineering. (level 1) |

| PO10 | Engineers analyzing JFET operation, biasing, and applications need to communicate their findings through clear and comprehensive reports and documentation. (level 2)                                                                                                                               |

| PO11 | Students can get demonstrate knowledge and understanding of the electronic devices and circuits and apply these to one's own project, as a member and leader in a team, to manage projects and in multidisciplinary environments.(level 2)                                                          |

| PSO1 | Students are able to explore the design of electronic devices in the areas of VLSI design and embedded systems. (level 3) |

|------|---------------------------------------------------------------------------------------------------------------------------|

| PSO2 | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)                              |

C211.4 Ability to demonstrate special purpose devices like Zener, Tunnel, varactor diode, UJT, SCR. (Understanding, Applying)

|      | Justification                                                                                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO1  | Students get the knowledge on special purpose devices like Zener, Tunnel, varactor diode, UJT, SCR to simplify the complex circuits for analysis. (level 2)                                                                                                                                         |

| PO3  | Students can design the special purpose devices like Zener, Tunnel, varactor diode, UJT, SCR .(level 2)                                                                                                                                                                                             |

| PO4  | Student can solve different complex electronic circuits design with the knowledge of special purpose devices.( level2)                                                                                                                                                                              |

| PO6  | Engineers must be aware of the broader impact of their work and strive to balance technical excellence with social responsibility. (level 1)                                                                                                                                                        |

| PO7  | Students must know that engineers need to consider the efficiency, reliability, and environmental impact of these circuits during the design and analysis phase. (level 1)                                                                                                                          |

| PO8  | Students can gain knowledge that engineers must prioritize integrity, safety, environmental responsibility, social impact, and transparency in their designs and analyses, ensuring that their work aligns with the highest standards of professional ethics in the field of engineering. (level 1) |

| PO10 | Engineers demonstrating special purpose devices like Zener diodes, Tunnel diodes, varactor diodes, UJTs, and SCRs need to communicate their findings through clear and comprehensive reports and documentation. (level 2)                                                                           |

| PO11 | Students can get demonstrate knowledge and understanding of the electronic devices and circuits and apply these to one's own project, as a member and leader in a team, to manage projects and in multidisciplinary environments.(level 2)                                                          |

| PO12 | Students can continuously learning to explore more knowledge in semiconductor devices. (level 3)                                                                                                                                                                                                    |

| PSO1 | Students are able to explore the design of electronic devices in the areas of VLSI design and embedded systems. (level 3)                                                                                                                                                                           |

| PSO2 | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)                                                                                                                                                                                                        |

C211.5 Ability to design and analyze the Small signal low frequency of BJT amplifiers. (Understanding, Creating, Applying)

|            | Justification                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------|

| PO1        | Students get the knowledge on Transistor Hybrid model to simplify the complex circuits for analysis (level 2) |

| PO2        | Students can analyze the operation of BJT amplifiers using transistor hybrid model. (level 3)                 |

| PO5        | Students can apply small signal model techniques in the design of FET amplifiers(level 3)                     |

| PO6        | Engineers must be aware of the broader impact of their work and strive to balance technical                   |

|            | excellence with social responsibility. (level 1)                                                              |

| <b>PO7</b> | Students must know that engineers need to consider the efficiency, reliability, and                           |

|            | environmental impact of these circuits during the design and analysis phase. (level 1)                        |

| <b>PO8</b> | Students can gain knowledge that engineers must prioritize integrity, safety, environmental                   |

|            | responsibility, social impact, and transparency in their designs and analyses, ensuring that                  |

|             | their work aligns with the highest standards of professional ethics in the field of engineering. |

|-------------|--------------------------------------------------------------------------------------------------|

|             | (level 1)                                                                                        |

| PO9         | Understanding and designing BJT amplifiers involve integrating knowledge from electronics,       |

|             | signal processing, and possibly other fields. Collaborating in a multidisciplinary team allows   |

|             | for a more comprehensive analysis, incorporating varied perspectives and expertise. (level 2)    |

| <b>PO10</b> | Effective communication skills are integral to successful engineering practices, especially      |

|             | when designing and analyzing complex systems like small signal low-frequency BJT                 |

|             | amplifiers. (level 2)                                                                            |

| PO11        | Students can get demonstrate knowledge and understanding of the electronic devices and           |

|             | circuits and apply these to one's own project, as a member and leader in a team, to              |

|             | manage projects and in multidisciplinary environments(level 2)                                   |

| <b>PO12</b> | Students can continuously learning to explore more knowledge in semiconductor devices.           |

|             | (level 2)                                                                                        |

| PSO1        | Students are able to explore the design of electronic devices in the areas of VLSI design and    |

|             | embedded systems. (level 3)                                                                      |

| PSO2        | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)     |

### C211.6 Ability to Design and analyze FET amplifiers (Understanding ,Creating, Applying)

|            | Justification                                                                                                                                                                                                                                                                                                         |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PO1        | Student get the knowledge on FET amplifiers to simplify complex circuit analysis .( level 3)                                                                                                                                                                                                                          |

| PO2        | Students can analyze the operation of FET amplifiers using small signal model. (level 3)                                                                                                                                                                                                                              |

| PO3        | Students can design the Transistor Hybrid model circuits for different transistor configurations.(level 3)                                                                                                                                                                                                            |

| PO5        | Students can apply transistor hybrid model techniques in the design of BJT amplifiers(level 3)                                                                                                                                                                                                                        |

| PO6        | Engineers must be aware of the broader impact of their work and strive to balance technical excellence with social responsibility. (level 1)                                                                                                                                                                          |

| <b>PO7</b> | Students must know that engineers need to consider the efficiency, reliability, and environmental impact of these circuits during the design and analysis phase. (level 1)                                                                                                                                            |

| PO8        | Students can gain knowledge that engineers must prioritize integrity, safety, environmental responsibility, social impact, and transparency in their designs and analyses, ensuring that their work aligns with the highest standards of professional ethics in the field of engineering. (level 1)                   |

| PO9        | The ability to design small signal low-frequency BJT amplifiers requires individual competence in understanding electronic circuit theory, BJT characteristics, and amplifier design principles. Engineers must independently analyze specifications and constraints to create effective amplifier designs. (level 2) |

| PO10       | Engineers involved in the design and analysis of FET amplifiers need to communicate their findings through clear and comprehensive reports and documentation. (level 2)                                                                                                                                               |

| PO11       | Students can get demonstrate knowledge and understanding of the electronic devices and circuits and apply these to one's own project, as a member and leader in a team, to manage projects and in multidisciplinary environments.(level 2)                                                                            |

| PSO1       | Students are able to explore the design of electronic devices in the areas of VLSI design and embedded systems. (level 3)                                                                                                                                                                                             |

| PSO2       | Students can solve the design problems of electronic devices using Keil and Xilinx.(level 3)                                                                                                                                                                                                                          |

## JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

### ACADEMIC CALENDAR 2022-23

## B. Tech./B.Pharm. II YEAR I & II SEMESTERS

### I SEM

| S. No | Description                                                                | Duration   |                      |  |

|-------|----------------------------------------------------------------------------|------------|----------------------|--|

|       |                                                                            | From       | То                   |  |

| 1     | Commencement of I Semester classwork                                       | 28.11.2022 |                      |  |

| 2     | 1 <sup>st</sup> Spell of Instructions                                      | 28.11.2022 | 21.01.2023 (8 Weeks) |  |

| 3     | First Mid Term Examinations                                                | 23.01.2023 | 30.01.2023 (1 Week)  |  |

| 4     | Submission of First Mid Term Exam Marks to the University on or before     | 45         | 04.02.2023           |  |

| 5     | 2 <sup>nd</sup> Spell of Instructions                                      | 31.01.2023 | 29.03.2023 (8 Weeks) |  |

| 6     | Second Mid Term Examinations                                               | 31.03.2023 | 08.04.2023 (1 Week)  |  |

| 7     | Preparation Holidays and Practical Examinations                            | 10.04.2023 | 15.04.2023 (1 Week)  |  |

| 8     | Submission of Second Mid Term Exam<br>Marks to the University on or before |            | 15.04.2023           |  |

| 9     | End Semester Examinations                                                  | 17.04.2023 | 29.04.2023 (2 Weeks) |  |

Note: No. of Working / Instructional Days: 93

### II SEM

| S. No | Description                                                                | Duration                    |                       |  |

|-------|----------------------------------------------------------------------------|-----------------------------|-----------------------|--|

|       |                                                                            | From                        | То                    |  |

| 1     | Commencement of II Semester classwork                                      | 01.05.2023                  |                       |  |

| 2     | 1 <sup>st</sup> Spell of Instructions (including Summer Vacation)          | 01.05.2023                  | 08.07.2023 (10 Weeks) |  |

| 3     | Summer Vacation                                                            | 15.05.2023                  | 27.05.2023 (2 Weeks)  |  |

| 4     | First Mid Term Examinations                                                | 10.07.2023                  | 15.07.2023 (1 Week)   |  |

| 5     | Submission of First Mid Term Exam Marks to the University on or before     |                             | 22.07.2023            |  |

| 6     | 2 <sup>nd</sup> Spell of Instructions                                      | 18.07.2023                  | 11.09.2023 (8 Weeks)  |  |

| 7     | Second Mid Term Examinations                                               | 12.09.2023 16.09.2023 (1 We |                       |  |

| 8     | Preparation Holidays and Practical Examinations                            | 19.09.2023                  | 23.09.2023 (1 Week)   |  |

| 9     | Submission of Second Mid Term Exam<br>Marks to the University on or before |                             | 23.09.2023            |  |

| 10    | End Semester Examinations                                                  | 25.09.2023                  | 07.10.2023 (2 Weeks)  |  |

Note: No. of Working / Instructional Days: 92

REGISTRAR

(An Autonomous Institution under UGC) Accredited by NAAC A+ Grade, Recognized under 2(f) of UGC Act 1956.

(Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda(V), Ibrahimpatnam(M), Ranga Reddy Dist., Telangana – 501 510

https://siiet.ac.in/

Sheriguda(Vill), Ibrahimpatnam R R Dist Telanoana -501 510

## DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING Class Timetable

CLASS: II-B.Tech ECE-A A.Y:2022-23 SEMESTER: I LH: C-101 TIME/ I II III IV V VI VII 1:00-1:30 DAY 10:30 -11:20 9:40-10:30 11:20-12:10 12:10-1:00 1:30-2:20 2:20-3:10 3:10-4:00 MON EDC COI EDC LAB / DSD LAB DSD NATL SPORTS TUE PTSP NATL DSD COI EDC SS DSD(T)/SS(T) L WED SS U PTSP DSD LAB / BS LAB DSD SS(T) EDC(T) EDC N THU NATL PTSP COI EDC(T) DSD(T) С SS DSD COUN H FRI SS EDC COI PTSP LIB CO-CU/DAA SAT EDC DSD SS NATL PTSP BS LAB / EDC LAB \*(T) - Tutorial Concern Faculty Course Course Name of the Course Course Name of the Code Name Faculty Code Name Faculty EDC-Electronic Devices EDC LAB - Electronic EC301PC K.Rajender EC306PC K.Rajender/B.Ashwini/M.Srilatha and Circuits Devices and Circuits Lab NATL-Network Analysis DSD LAB - Digital System EC302PC M.Nagaraju EC307PC G.Anusha/T.Divya/P.Krishna Rao and Transmission Lines Design Lab **DSD-Digital System** BS LAB - Basic Simulation EC303PC G.Anusha EC308ES P.Rajendra/T.Naresh Design Lab EC304PC SS-Signals and Systems P.Rajendra LIB Library B.Ashwini/Dr.K.Srinivasa Reddy PTSP-Probability Theory EC305ES T.Naresh COUN and Stochastic Processes Counseling K.Rajender/G.Anusha/G.Anitha CO-CU/DAA Co-Curricular/Dept.Assc.Act. K.Rajender/T.Naresh/D.Aruna COI-Constitution of India \*MC309 S.Swapna SPORTS Sports G.Anitha/P.Sumana PRINCIPAL Sti Indu Institute Breingredung & Tech Class Incharge Head of The Department

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

### **LESSON PLAN**

| Programme: B.Tech                             | Academic Year: 2022-23        |

|-----------------------------------------------|-------------------------------|

| Year: II                                      | Semester: I                   |

| Course Title: Electronic devices and circuits | Course Code: EC301PC          |

| Name of Faculty: K.Rajender                   | Number of lectures per week:3 |

### **Unit-I Syllabus**

**Diode and Applications:** Diode - Static and Dynamic resistances, Equivalent circuit, Load line analysis, Diffusion and Transition Capacitances, Diode Applications: Switch-Switching times. Rectifier - Half Wave Rectifier, Full Wave Rectifier, Bridge Rectifier, Rectifiers with Capacitive and Inductive Filters, Clippers-Clipping at two independent levels, Clamper-Clamping Circuit Theorem, Clamping Operation, Types of Clampers.

| No. of                                                                                                | Topics                                               | Reference | Teaching |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------|----------|

| Sessions                                                                                              |                                                      |           | Method/  |

| Planned                                                                                               |                                                      |           | Aids     |

| 01                                                                                                    | Diode - Static and Dynamic resistances               | T1, R 2   | BB,      |

| 02                                                                                                    | Equivalent circuit, Load line analysis               | T1, R 2   | BB       |

| 01                                                                                                    | Diffusion and Transition Capacitances                | T1, R 2   | BB,PPT   |

| 01                                                                                                    | Diode Applications: Switch-Switching times           | T1, R 2   | BB       |

| 02                                                                                                    | Rectifier - Half Wave Rectifier, Full Wave Rectifier | T1, R 2   | BB,PPT   |

| 01                                                                                                    | Bridge Rectifier                                     | T1, R 2   | BB       |

| 02                                                                                                    | Rectifiers with Capacitive and Inductive Filters     | T1, R 2   | BB       |

| 01                                                                                                    | Clippers-Clipping at two independent levels          | R 3,W1    | BB       |

|                                                                                                       | Clamper-Clamping Circuit Theorem, Clamping           |           | BB       |

| 02                                                                                                    | Operation, Types of Clampers.                        | R 3,W2    |          |

| Gap beyor                                                                                             | nd syllabus(if any):                                 |           |          |

| Gap within                                                                                            | n the syllabus(if any)                               |           |          |

| <b>Course Outcome 1:</b> Describe the applications of diode as rectifier, clippers, clamper Circuits. |                                                      |           |          |

\*Session Duration: 50 minutes

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

| Course Title: Electronic devices and circuits | Course Code: EC301PC |

|-----------------------------------------------|----------------------|

| Course The. Electronic devices and chedits    | Course Code. LC3011C |

### **Unit-II Syllabus**

**Bipolar Junction Transistor (BJT):** Principle of Operation, Common Emitter, Common Base and Common Collector Configurations, Transistor as a switch, switching times, Transistor Biasing and Stabilization - Operating point, DC & AC load lines, Biasing - Fixed Bias, Self Bias, Bias Stability, Bias Compensation using Diodes.

| No. of                                                                                      | Topics                                                 | Reference | Teaching |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------|----------|

| Sessions                                                                                    |                                                        |           | Method/  |

| Planned                                                                                     |                                                        |           | Aids     |

| 01                                                                                          | Principle Operation of BJT                             | T1,R 2    | BB       |

| 01                                                                                          | Common Emitter Configuration                           | T2,W3     | BB,PPT   |

| 02                                                                                          | Common Base and Common Collector Configurations        | T1,R 2    | BB,PPT   |

| 01                                                                                          | Transistor as a switch, switching times                | T1,R 1    | BB       |

| 01                                                                                          | Transistor Biasing and Stabilization - Operating point | T1,R 2    | BB,PPT   |

| 02                                                                                          | DC & AC load lines                                     | T2,R 2    | BB       |

| 01                                                                                          | Biasing - Fixed Bias                                   | T1, W4    | BB       |

| 02                                                                                          | Self Bias, Bias Stability                              | T1, R 2   | BB       |

| 02                                                                                          | Bias Compensation using Diodes                         | T2, R 2   | BB       |

| Gap beyond syllabus(if any):                                                                |                                                        |           |          |

| Gap within the syllabus(if any)                                                             |                                                        |           |          |

| Course Outcome 1: Design various switching devices such as, transistor , Transistor biasing |                                                        |           |          |

\*Session Duration: 50 minutes

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

Course Title: Electronic devices and circuits Course Code: EC301PC

### **Unit-III Syllabus**

**Junction Field Effect Transistor (FET):** Construction, Principle of Operation, Pinch-Off Voltage, Volt-Ampere Characteristic, Comparison of BJT and FET, Biasing of FET, FET as Voltage Variable Resistor. **Special Purpose Devices:** Zener Diode - Characteristics, Voltage Regulator. Principle of Operation - SCR, Tunnel diode, UJT, Varactor Diode

| No. of                          | Topics                                                                                                          | Reference | Teaching |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------|----------|--|

| Sessions                        |                                                                                                                 |           | Method/  |  |

| Planned                         |                                                                                                                 |           | Aids     |  |

| 02                              | Construction and Principle Operation of FET                                                                     | T1, R1    | BB       |  |

| 02                              | Pinch-Off Voltage, Volt-Ampere Characteristic                                                                   | T2, R2    | BB       |  |

| 01                              | Comparison of BJT and FET                                                                                       | T1, R 1   | BB       |  |

| 02                              | Biasing of FET, FET as Voltage Variable Resistor                                                                | T1, R 2   | BB       |  |

| 01                              | Zener Diode - Characteristics                                                                                   | T2, R 2   | BB, PPT  |  |

| 01                              | Voltage Regulator                                                                                               | T1, R 1   | BB       |  |

| 01                              | Principle of Operation – SCR                                                                                    | T1, W5    | BB,PPT   |  |

| 01                              | Tunnel diode                                                                                                    | T2, W6    | BB,PPT   |  |

| 02                              | UJT, Varactor Diode                                                                                             | T1, R2    | BB,PPT   |  |

| Gap beyo                        | Gap beyond syllabus(if any):                                                                                    |           |          |  |

| Gap within the syllabus(if any) |                                                                                                                 |           |          |  |

|                                 | <b>Course Outcome 1:</b> Analyze the operation FET ,Special Devices like Zener, Tunnel, varactor diode,UJT,SCR. |           |          |  |

\*Session Duration: 50minutes

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

| Course Title: Electronic devices and circuits | Course Code: EC301PC |

|-----------------------------------------------|----------------------|

| Course Thie. Electronic devices and chedits   |                      |

### **Unit-IV Syllabus**

**Analysis and Design of Small Signal Low Frequency BJT Amplifiers:** Transistor Hybrid model, Determination of h-parameters from transistor characteristics, Typical values of h-parameters in CE, CB and CC configurations, Transistor amplifying action, Analysis of CE, CC, CB Amplifiers and CE Amplifier with emitter resistance, low frequency response of BJT Amplifiers, effect of coupling and bypass capacitors on CE Amplifier.

| No. of                                                   | Topics                                                          | Reference | Teaching |

|----------------------------------------------------------|-----------------------------------------------------------------|-----------|----------|

| Sessions                                                 |                                                                 |           | Method/  |

| Planned                                                  |                                                                 |           | Aids     |

| 02                                                       | Transistor Hybrid model                                         | T1, R2    | BB       |

| 02                                                       | Determination of h-parameters from transistor characteristics   | T2, R1    | BB       |

| 01                                                       | Typical values of h- parameters in CE, CB and CC configurations | T1, R2    | BB       |

| 01                                                       | Transistor amplifying action                                    | T1, R1    | BB       |

| 01                                                       | Analysis of CE Amplifier                                        | T1, R1    | BB       |

| 01                                                       | Analysis of CB Amplifier                                        | T1, R1    | BB       |

| 01                                                       | Analysis of CC Amplifier                                        | T1, R1    | BB       |

| 02                                                       | Analysis of CE Amplifier with emitter resistance                | T1,W7     | BB       |

| 01                                                       | low frequency response of BJT Amplifiers                        | T2,W8     | BB,PPT   |

| 01                                                       | effect of coupling and bypass capacitors on CE<br>Amplifier     | T1, R2    | BB       |

| Gap beyond syllabus(if any):                             |                                                                 |           |          |

| Gap within the syllabus(if any)                          |                                                                 |           |          |

| Course Outcome 1: Define explain Transistor Hybrid model |                                                                 |           |          |

\*Session Duration: 50minutes

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

Course Title: Electronic devices and circuits Course Code: EC301PC

### **Unit-V Syllabus**

**FET Amplifiers:** Small Signal Model, Analysis of JFET Amplifiers, Analysis of CS, CD, CG JFET Amplifiers. MOSFET Characteristics in Enhancement and Depletion mode, Basic Concepts of MOS Amplifiers.

| No. of   | Topics                                                                    | Reference | Teaching |  |

|----------|---------------------------------------------------------------------------|-----------|----------|--|

| Sessions |                                                                           |           | Method/  |  |

| Planned  |                                                                           |           | Aids     |  |

| 02       | Small Signal Model                                                        | T1, R2    | BB       |  |

| 01       | Analysis of JFET Amplifiers                                               | T2, R2    | BB       |  |

| 02       | Analysis of CS JFET Amplifiers                                            | T1, W9    | BB       |  |

| 01       | Analysis of CD JFET Amplifiers                                            | T1, W10   | BB       |  |

| 01       | Analysis of CG JFET Amplifiers                                            | T2, R 1   | BB       |  |

| 02       | MOSFET Characteristics in Enhancement mode                                | T1, R 2   | BB       |  |

| 02       | MOSFET Characteristics in Depletion mode                                  | T2, R 1   | BB       |  |

| 02       | Basic Concepts of MOS Amplifiers                                          | T2, R 2   | BB       |  |

| Gap beyo | Gap beyond syllabus(if any):                                              |           |          |  |

| Gap with | Gap within the syllabus(if any)                                           |           |          |  |

| Course O | Course Outcome 1: Draw the operation of small signal model FET operation. |           |          |  |

\*Session Duration: 50minutes

\*Total Number of Hours/Unit: 13

### **Text Books:**

- 1. Electronic Devices and Circuits- Jacob Millman, McGraw Hill Education

- 2. Electronic Devices and Circuits theory– Robert L. Boylestead, Louis Nashelsky, 11<sup>th</sup> Edition, 2009, Pearson.

### **Reference Books:**

- 1. The Art of Electronics, Horowitz, 3<sup>rd</sup> Edition Cambridge University Press

- 2. Electronic Devices and Circuits, David A. Bell 5<sup>th</sup> Edition, Oxford.

- 3. Pulse, Digital and Switching Waveforms –J. Millman, H. Taub and Mothiki S. Prakash Rao, 2Ed., 2008, Mc Graw Hill.

### Web References for Electronic devices and circuits:

| S.NO | WEB LINK                                                                                                                           |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1    | https://www.electronics-tutorials.ws/diode/diode-clipping-circuits.html                                                            |

| 2    | https://www.physics-and-radio-electronics.com/electronic-devices-and-<br>circuits/rectifier/clampercircuits.html                   |

| 3    | https://www.electronics-tutorials.ws/amplifier/amp_2.html                                                                          |

| 4    | https://www.electronics-tutorials.ws/amplifier/transistor-biasing.html                                                             |

| 5    | https://www.daenotes.com/electronics/industrial-electronics/silicon-<br>controlled-rectifiers-scr                                  |

| 6    | https://www.physics-and-radio-electronics.com/electronic-devices-and-<br>circuits/semiconductor-diodes/tunneldiode-howitworks.html |

| 7    | https://www.slideshare.net/syedafroz1234/common-emitter-with-emi                                                                   |

| 8    | https://unacademy.com/lesson/low-frequency-analysis-of-bjt-<br>amplifier/5TUKWO6Z                                                  |

| 9    | http://www.mhhe.com/engcs/electrical/neamen01/ch06.pdf                                                                             |

| 10   | https://www.coursehero.com/file/ph9hsb/UNIT-III-FET-Amplifiers-<br>Analysis-of-JFET-Amplifiers-Analysis-of-CS-CD-CG-JFET/          |

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

Lecture notes

### Unit 1 link: <u>https://drive.google.com/file/d/1CRNQMLV6wrWe4gKGPB\_T9aANVmiEsDjy/view?</u> <u>usp=sharing</u>

Unit 2 link: https://drive.google.com/file/d/13ju0qaLBFIoUEven9cnH7sl3yONo-U19/view?usp=sharing

### Unit 3 link:

https://drive.google.com/file/d/1E6YT7W7GNVI-YmJE9M-aTYW6-NSDdFkE/view?usp=sharing

### Unit 4 link:

https://drive.google.com/file/d/13olKNFwTtnpLVs\_9fi4JnPADivwGTxl\_/view?usp=sharing

### Unit 5 link:

https://drive.google.com/file/d/1tR2whxV6YK1SFfV\_DLKvIfFvKQXZP7aq/view?usp =sharing

Accredited by NAAC with A+ Grade, Recognized under 2(f) of UGC Act 1956 (Approved by AICTE, New Delhi and Affiliated to JNTUH, Hyderabad) Khalsa Ibrahimpatnam, Sheriguda (V), Ibrahimpatnam (M), Ranga Reddy Dist., Telangana – 501 510 Website: https://siiet.ac.in/

### **Power point presentation**

**PPT link:**

https://docs.google.com/presentation/d/1vcLrryBksZjVWcD08MtySVjBxz6-Hrgl/edit?usp=sharing&ouid=106700162151853541587&rtpof=true&sd=true

https://docs.google.com/presentation/d/1cL6gOnDCowYbCph1mBac9LBhY-F8ccT4/edit?usp=sharing&ouid=106700162151853541587&rtpof=true&sd=true

https://docs.google.com/presentation/d/1GFPEI6lLkdW0MBaTvfjWoHkbDIzCb\_SZ /edit?usp=sharing&ouid=106700162151853541587&rtpof=true&sd=true

**R15** Code No: 123AU JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD B. Tech II Year I Semester Examinations, November/December - 2016 ELECTRONIC DEVICES AND CIRCUITS (Common to EEE, ECE, CSE, EIE, IT, ETM, MCT)

### Time: 3 Hours

**Note:** This question paper contains two parts A and B. Part A is compulsory which carries 25 marks. Answer all questions in Part A. Part B consists of 5 Units. Answer any one full question from each unit. Each question carries 10 marks and may have a, b, c as sub questions.

### PART-A

|      |                                                    | (25 Marks) |

|------|----------------------------------------------------|------------|

| 1.a) | Define static and dynamic resistance of P-N diode. | [2]        |

| b)   | Explain about Zener break down.                    | [3]        |

| c)   | Define ripple factor.                              | [2]        |

| d)   | Explain about voltage regulation.                  | [3]        |

| e)   | What are the applications of UJT?                  | [2]        |

| f)   | What do you mean by early effect?                  | [3]        |

| g)   | Explain about collector feedback bias.             | [2]        |

| h)   | Write about thermal runaway.                       | [3]        |

| i)   | Mention small signal parameters of JFET.           | [2]        |

| j)   | Differentiate between BJT and JFET.                | [3]        |

### **PART-B**

### (50 Marks)

- 2.a) Compare the characteristics of PN junction diode, Zener Diode and Tunnel diode.

- For a Ge diode, the  $I_0=2\mu A$  and the voltage of 0.26V is applied. Calculate the b) forward and reverse dynamic resistance values at room temperature. [5+5]

- OR

- 3.a) Derive an expression for transition capacitance of a diode.

- Explain Avalanche and Zener Breakdowns. b) [5+5]

- 4.a) Explain the operation of Full Wave Rectifier with Induction filter with necessary diagrams.

- A diode whose internal resistance is  $20\Omega$  is to supply power to a  $100\Omega$  load from b) 110V (R.M.S) source of supply. Calculate:

- i) Peak Load Current

- ii) DC Load Current

- iii) AC Load Current

- iv) % Regulation from No load to given load. [5+5]

### OR

#### Explain the operation of Full Wave Rectifier with necessary graphs. 5.a)

A  $3K\Omega$  resistive load is to be supplied with a D.C. voltage of 300V from A.C. b) voltage of adequate magnitude and 50Hz frequency by wave rectification. The LC filter is used along the rectifier. Design the bleeder resistance, turns ratio of transformer, VAWWW of MathaRaSiVratingSf diGQ. 1n [5+5]

Max. Marks: 75

- 6.a) Derive Emitter Efficiency, Transport factor and large signal current gain and derive the relation between them.

- b) Explain how transistor works as an amplifier? [5+5]

OR

- 7.a) Explain the operation of CC Configuration of BJT and its input and output characteristics briefly.

- b) Explain about Punch through and Base width modulation. [5+5]

- 8.a) What is Biasing? Explain the need of it. List out different types of biasing methods.

- b) In a Silicon transistor circuit with a fixed bias,  $V_{CC}=9V, R_{C}=3K\Omega, R_{B}=8K\Omega, \beta=50, V_{BE}=0.7V.$ Find the operating point and Stability factor. [5+5]

#### OR

9.a) Derive the expression for stability factor of self bias circuit.

- b) Explain in detail about Thermal Runaway and Thermal Resistance. [5+5]

- 10.a) Why we call FET as a Voltage Controlled Device.

- b) For the Common Source Amplifier, calculate the value of the voltage gain, given

i) r<sub>d</sub>=100KΩ, R<sub>L</sub>=10KΩ, g<sub>m</sub>=300µ and R<sub>O</sub>=9.09KΩ.

ii) If C<sub>DS</sub>=3pF, determine the output impedance at a signal frequency of 1 MHz.

[5+5]

### OR

- 11.a) Define DC Drain resistance, AC Drain Resistance, Amplification Factor and derive them.

- b) What are the values of  $I_D$  and  $g_m$  for  $V_{GS} = -0.8V$  if  $I_{DSS}$  and  $V_P$  are given as 12.4mA and -6V respectively? [5+5]

--00000--